Bulldozer

Présentation et concepts avancés de la nouvelle architecture CPU.

Introduction

De nos jours, la recherche sur les CPUs se concentre sur la puissance, mais avec une gestion de l'énergie contrôlée. Il n'est pas rare maintenant de voir l'apparition de produits "green" en hardware. Cependant que ce soit sur le marché ou pour le développement de nouveux concepts, le maître reste Intel et AMD campe à la seconde place.

Initié "from scratch" par AMD en 2003, Bulldozer est une tentative d'innovation de la firme Californienne dans le nano monde des microprocesseurs. Alors qu'auparavant il se contentait de suivre Intel et de plus ou moins copier ses technologies, AMD tente l'innovation avec sa nouvelle microarchitecture.

À la différence de ses précédents processeurs, K15 n'est pas basé sur l'ancêtre K7, vieux de plus de 10 ans. Complètement nouvelle et innovante, elle apporte de nouveaux concepts auxquels nous allons nous intéresser.

Concepts

Bulldozer est une architecture qui mise sur le partage des ressources et les hautes fréquences. Malgré tout, la puissance brute est en retrait par rapport aux processeurs K10 à nombres de cores égaux.

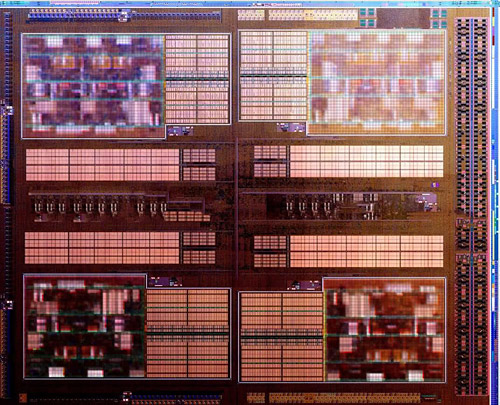

Le concept principal : les modules. Créés par AMD dans un esprit d'évolutivité et de modularité, les modules sont au centre de Bulldozer. Ils sont composés de 213M de transistors sur un die de 30,9 mm²

Le Cluster Multi-Threading est la deuxième composante de ce nouveau système. Nous le verrons ensuite, le CMT parle de ressources dédiées et partagées entre les cores d'un module. L'intérêt de partager des ressources matérielles réside dans le fait de pouvoir économiser les transistors sur le die, mais aussi de diminuer ainsi la puissance dissipée par la puce, tout en s'efforçant de maintenir un niveau de performances proches de celles de ressources dédiées. Alors que jusqu'ici on avait du multithreading par cores (exécution de 2 threads), ou la multiplication des cores, Bulldozer est entre les deux.

Le Turbo Core a été amélioré. Cette technologie consiste à permettre l'augmentation temporaire de la fréquence d'un core en fonction de l'état (utilisation, température...) des autres cores.

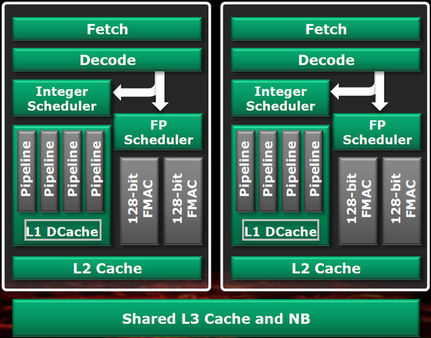

Module et CMT

Un module est une nouvelle définition d'un "core". Dans un module Bulldozer, on retrouve 2 cores qui partagent des ressources avec le CMT. On peux observer un seul front-end pour les cores, ce qui permet d'économiser de l'énergie car cette partie est une grosse consommatrice et des transistors. AMD a remarqué que le Floating Point Unit était utilisé à 50% du temps dans une architecture classique. Par conséquent, il est ici partagé entre les deux cores du module. À noter qu'un core peux utliser l'ensemble des ressources d'un module.

Un module est ainsi beaucoup moins gros et consommateur d'énergie que deux cores classiques. On obient une économie de 50% en surface pour 80% des performances de deux cores complets.

En détails

Le front end est un composant clé qui alimente les deux cores du module bulldozer en instructions. Sur celui-ci, AMD a travaillé sur l'efficacité de l'exécution des instructions. Cela passe par de la prédiction de branchements, des détecteurs de boucle, de la prédiction hybride (selon la porté locale ou globale des données) ou un emplacement de stockage des adresses de retour.

L'unité de décodage a été élargie par rapport à K10. Elle décode maintenant 4 instructions par cycle, contre 3 auparavant. Grâce à un méchanisme de fusion du décodage de certains couples (par exemple une comparaison suivie d'un saut), cette unité peux exécuter jusqu'à 5 instructions par cycle.

Les unités de calculs nombre entier sont composées de deux Arithmetic Logic Unit (ALU) et de deux Address Generation Units (AGU).

L'unité de calcul nombres flottants dont nous avons parlé auparavant est donc partagée entre les deux cores et est capable d'effectuer des produits scalaires (utiles en calculs graphiques). Elle est suffisamment grande pour faire des calculs sans arrondis, permettant une précision accrue.

Les caches sont des zones mémoires (très) rapides en accès. Du fait de leur coûts de fabrication élevé, elles sont d'autant plus petites qu'elles sont près des cores. On retrouve actuellement 3 types de caches allant de L1 à L3. Le fonctionnement habituel des caches repose sur une relation exclusive, c'est à dire que les caches successifs ne contiennent pas les mêmes données. Dans Bulldozer, il y a une relation inclusive entre L1 et L2. Par un processus de write-through (opposé au write-back), les données copiées dans L1 le sont aussi dans L2 (opposé au fait de copier les données dans L2 uniquement si elles sont évincées de L1). Ainsi, si une donnée est évincée de L1, il n'y a pas besoin de la réécrire dans L2. Cependant, cela implique plus d'écritures dans L2. Pour pallier à ça, il existe un cache WCC (Write Coalescing Cache) qui une fois plein, passe sont contenu dans L2, permettant ainsi une seul écriture. Enfin vient le cache L3, seul victime cache dans le module, qui reçoit les données évincées du L2. Un nouveau problème se pose alors : lorsqu'une donnée et copiée de L3 à L1, elle ne l'est pas dans L2. Il peut alors y avoir des problème de cohérences dans les données. Un méchanisme existe pour vérifier cette cochérence, appellée cache snooping. Cette technique est très consommatrice en bande passante et on ne sait pas comment ce problème de ralentissement a été géré par AMD.

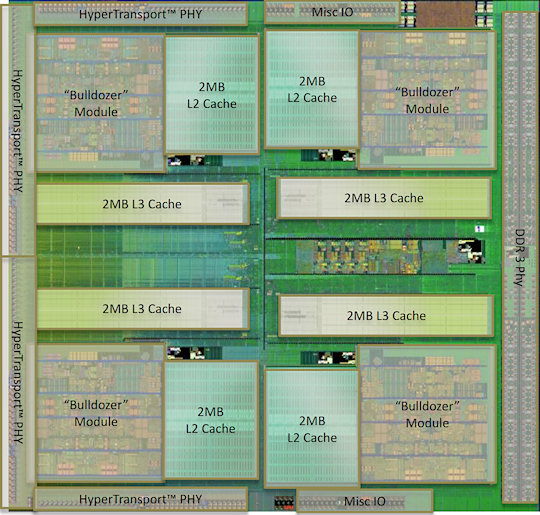

CPU Bulldozer

Assemblons les données vues précédemment et construisont un CPU Bulldozer :

- 2+ modules (2 cores + cache L1/L2)

- Cache L3

- Contrôleur mémoire

- Contrôleur de bus

Voici une petite comparaison entre deux processeurs AMD, génération K15 et dernière génération K10.

| AMD FX | Phenom II x6 |

|---|---|

|

|

On remarque que les nouvelles générations offrent un nombre de transistores bien plus élevés (AMD avait annoncé 2 Milliards mais est revenu sur sa déclaration), sur un die plus petits et avec une fréquence revue à la hausse