Architecture Core i7

Core i7

Caracteristiques

Pour différencier les processeurs, ils existent plein de criteres :

- le jeu d’instructions : addition, multiplication, max(nb1,nb2)

- Nombre de bits : 32 ou 64

- Vitesse de l’horloge : nombre de cycles/ seconde

- Nombre de cœurs

- Nombre de transistors

La plupart du temps, les acheteurs ne s'intéressent qu'aux performances du processeur et aux nombres de coeurs, mais nous allons voir que les performances ont pu être améliorées cette fois ci en s'attaquant aux voies de communications autour du processeur.

En effet, le talon d'Achille des processeurs se situait au niveau des échanges avec les autres composants d'une tour notamment la mémoire.

Pour commencer Intel a pu mettre en place un réel processeur à quatre coeurs dans le sens ou avant les processeurs, les core Quad, étaient en réalité composés de deux puces stockant un processeur double coeur(dual Core) chacune.

Ce premier exploit a permis à Intel d'éliminer une certaine dose de latence : les processeurs étant sur 2 puces différentes devaient passer par le FSB pour communiquer et donc rajouter du trafic sur cette voie déjà bien utilisée.

HyperThreading

Qu'est ce que L'Hyper Threading? ou bien encore HT comme on peut le voir sur certains forums.

L'Hyper Threading est tout simplement du SMT (Simultaneous Multi Threading) à deux voies. Deux voies signifiant que chaque processeur recevra des instructions à traiter

par 2 threads et non plus un seul comme auparavant.

Ces deux threads partagent des données comme des registres, le cache le pipeline et le bus. Bien évidemment un système de contrôle a été mis en place

afin de gérer les deads-locks pouvant survenir. L'Hyper Threading est une technologie très répandue, il existe aussi du SMT à 4 voies, mais celui ci est plus généralement

utilisé pour des machines plus importants( super calculateur, serveur).

Cette technique permet d'accélérer le traitement des instructions et donc les performances des machines basées sur un Core i7. Il est possible de désactiver cette option

gourmande en énergie dans le bios.

En activant l'HT, l'OS (Operating System) perçoit le processeur comme un processeur à 8 coeurs et non plus 4. On dit que c'est un processeur à 8 coeurs logiques.

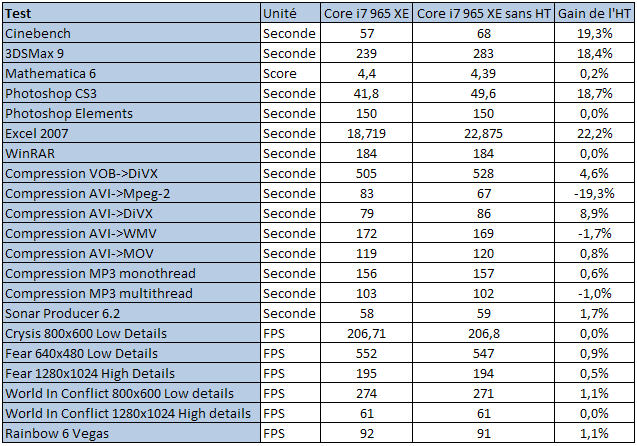

Ci dessous, un bench qui représente les différents gains ou perte de performances en fonction de l'utilisation :

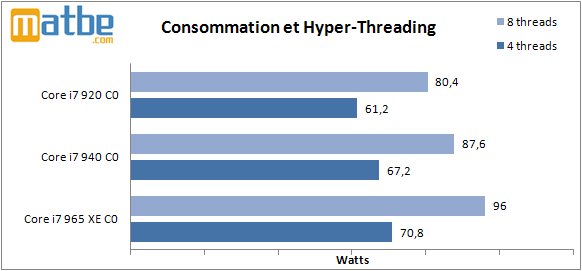

On peut voir ici que sur ces différents modèles que la consommation peut augmenter de plus de 20% en activant l'HT. Intel a pu annoncer des gains de performances

pouvant s'élever à 33% mais le benchmark ci dessous permet de mettre des points d'interrogation sur certaines utilisations de l'HT en fonction de l'utilisation personnelle

que l'on en fait.

IMC

L'IMC signifie Integrated Memory Controler. Son apparition intervient pour plusieurs raisons. Tout d'abord, le besoin grandissant de la quantité de mémoire et de son accès

(grâce à l'apparition de nouveaux processeurs de plus en plus puissant) a pu mener certains ingénieurs à penser qu'il fallait créer un canal dédié reliant la mémoire et le processeur.

Cette solution permet de diminuer la latence entre le processeur et la mémoire. La deuxième raison est que le canal FSB est déjà bien rempli par les autres requêtes du processeur.

Le fait de le soulager des accès mémoires permet une fois de plus d'améliorer la rapidité de la machine puisque l'on peut faire passer peu plus les autres données.

Cette apparition de l'IMC vient en même temps que la nouvelle gestion des caches par Intel.

En effet, avant le cache L1 était exclusif et les caches L2 et L3 étaient partagés. Désormais, seul le cache L3 est partagé.

Le cache L1 ne change pas, le cache L2 est aussi exclusif mais réduit de 6Mo à 256Ko et le cache L3 est seulement agrandi, il passe à 8 Mo.

Pourquoi changer une telle organisation ?

Tout d'abord il faut savoir que chaque coeur d'un processeur a plusieurs endroits où stocker les données : les registres et les caches. Nous allons nous consacrer aux caches.

Ces derniers permettent selon leur rôle de stocker de l'information ou l'adresse détenant l'information. Intel a décidé de réorganiser ces caches.

Le parti pris par Intel semble être le suivant :

Diminuer les recherches dans le cache par le processeur : avant il fallait sonder les caches L2 et L3 pour savoir ou se situait l'information désirée. Cela demandait

un certain temps. Le fait d'avoir un cache L3 qui contient tous les caches L2 permet d'interroger qu'un seul cache. Le processeur va donc interroger les deux premiers niveaux de cache.

Si jamais la donnée se trouve sur un autre coeur, il va consulter le cache L3 afin d'obtenir l'information.

En plus des avantages énoncés plus haut, l'IMC permet de gérer 3 canaux (DDR3) ce qui signifie gérer un trafic montant à 32 Go/s.

QPI

QPI ou encore Quick Path Interconnect.

La première question qui nous vient à l'esprit est : et pourquoi faire?

Le QPI est un bus inventé par Intel qui permet d'interconnecter les coeurs entre eux ainsi qu'au chipset. Son but est de remplacer le FSB.

Petit rappel du fonctionnement du FSB :

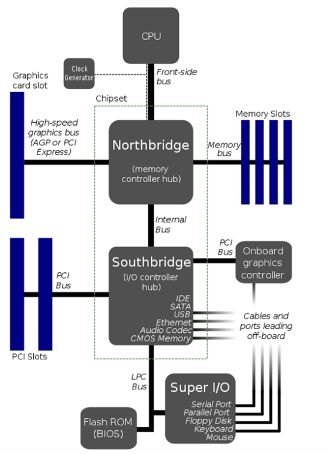

Comme on peut le voir sur cette image, le processeur doit faire transiter toutes ces requêtes et données via le FSB pour communiquer avec les composants.

Il existe bien évidemment un "aiguilleur" afin de fluidifier le trafic. Le premier composant servant d'aiguilleur est le NorthBridge.

Ce dernier doit faire le tri entre la mémoire, la carte graphique et le reste. Le reste est traité par le SouthBridge. Il s'occupe des autres composants.

Cela va de la simple prise USB, au clavier en passant par l'ethernet et le sata par exemple.

Le FSB, pour Front Side Bus, doit supporter un trafic très dense. Son débit maximal est de 12.8 Go/s et ce pour le seul canal existant. Toutes les écritures

et lectures en mémoire et sur les composants passent par ce FSB. Les utilisateurs et constructeurs ont bien compris que le talon d'Achille se situait ici.

C'est pourquoi Intel a mis en place son nouveau bus le QPI.

C'est un bus composé de deux voies. Il relie chaque coeur aux autres coeurs et au chipset. Le fait d'avoir deux voies autorise la lecture et l'écriture en même temps.

Le nouveau bus permet une largeur de bande de 20 bits dont 4 de CRC. Pour calculer la vitesse maximale théorique, il faut multiplier les données utiles

par la vitesse le nombre de transferts possible en 1 seconde. La fréquence de ce nouveau bus est de 6.4 G transferts/seconde.

6.4 * 16 / 8 = 12.8 Go/s ( on divise par 8 pour mettre le résultat en octets).

On retombe bien sur le même résultat que le FSB, sauf que ce débit est valable pour une seule voie. Les performances sont donc doublées puisqu'il y a deux voies,

le débit passe désormais à 25.6 Go/s. Au final, chaque coeur peut interroger le chipset ou un autre processeur avec ce débit. Sachant que l'IMC est intégré,

le QPI est un bus deux fois plus rapide et n'est plus ralenti par les accès mémoire.

Au final, le processeur est bien plus performant et le bus reliant le processeur

au chipset n'est plus le goulot d'étranglement.

Turbo Boost

Le Turbot Boost ou encore l'OverClocking automatique.

Le Turbo boost est une technologie qui permet de gérer l'utilisation des processeurs en fonction de la charge de travail à effectuer. Cela permet donc d'éviter de faire fonctionner

plusieurs coeurs lorsqu'un seul suffit. Si jamais ce seul coeur n'est pas suffisant, le Turbo Boost peut augmenter la fréquence du coeur utilisé et ceci à la volée

et de façon indépendante ( les autres coeurs ne sont pas affectés par ces changements). Afin de savoir comment augmenter la fréquence et dans quelle limite

augmenter cette fréquence, un composant nommé PCU pour Power Control Unit a accès à certaines données comme la température, le voltage et la fréquence de chaque coeur.

Cela permet donc de pouvoir manipuler chaque coeur indépendamment en garantissant la non détérioration du matériel.

Une vidéo sur le site d'Intel explique très bien ce principe et le met en image :

http://www.intel.com/technology/product/demos/turboboost/demo.htm?iid=tech_demo+tb .

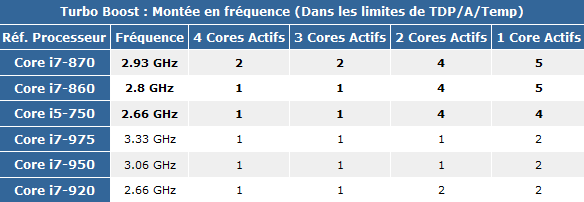

Evidemment cette augmentation de fréquence suit une certaine procédure. En fonction du nombre de coeurs actifs, il sera possible d'augmenter la fréquence de 133MHz

multiplié par un certain nombre. Si 1 coeur actif on augmente de X *133MHZ, si 2 coeurs actifs Y*133MHz... Ci dessous un exemple sur quelques processeurs :