CONCEPTION D'UN OS - Segmentation & Interruptions

Segmentation - Fonctionnement

La segmentation est un mécanisme de traduction d'adresses.Types d'adresses

En mode protégé, il existe 3 types d'adresses :

Adresse logique ou virtuelle :

Adresses utilisées directement par le coeur du processeur, et qui constituent les adresses mentionnées dans les programmes et le système d'exploitation.Adresse linéaire :

Cest simplement un déplacement (32 bits) par rapport au début de lespace dadressage du processus.Adresse physique :

Cest ladresse qui sera directement utilisé à lextérieur du processeur pour la manipulation de la mémoire (32 ou 36 bits).- La base, sur 32 bits, est l'adresse lineaire où debute le segment en memoire.

- La limite, sur 16 bits, definit la longueur du segment. Si le bit G est a 0, la limite est exprimee en octets, sinon, elle est exprimee en nombre de pages de 4 ko.

- Le type definit le type de segment, comme code, donnees ou pile.

- Le bit S est mis a 1 pour un descripteur de segment et a 0 pour un descripteur systeme

- Le DPL indique le niveau de privilege du segment. Le niveau 0 correspond au mode super-utilisateur.

- Le bit P est utilisé pour determiner si le segment est present en memoire physique. Il est a 1 si c'est le cas.

- Le bit D/B precise la taille des instructions et des donnees manipulees. Il est mis a 1 pour 32 bits.

- Le bit AVL est librement disponible.

- lgdt : charger le registre gdtr

- sgdt : stocker le registre gdtr

- lldt : charger le registre ldtr

- sldt : stocker le registre ldtr

|

|

|

Voyons plus en détail le mécanisme et surtout les éléments intervenant dans cette procédure de traduction.

Mécanisme

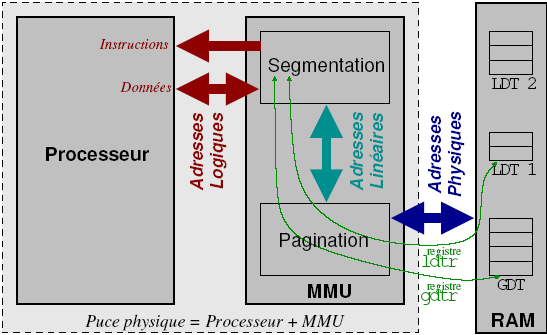

Voici un schéma présentant clairement le mécanisme de traduction des adresses :

La MMU (Memory Management Unit) est une puce particulière chargée de la traduction des adresses et donc dans notre cas, de la segmentation. Pour cela, elle utilise des tables de traduction lui permettant de faire le lien entre les adresses logiques et les adresses physiques : GDT et LDT. Nous y reviendrons dans la partie suivante.

NB : La MMU bien qu'indépendante est sur la même puce de silicium

Il est donc important de noter l'importance de la segmentation. Ainsi, le processeur ne travaille qu'avec des adresses logiques sans se soucier de l'adresse physique dont il délègue le traitement. Ce mécanisme permet de s'abstraire des adresses physiques manipulées par les programmes qui s'exécutent. Grâce à ce cela, il est possible d'avoir deux instances d'un programme qui possèdent la même adresse logique mais qui sont situés à des adresses physiques différentes.

Pour cela, il suffit de définir deux tables de traduction différentes pour chaque programme et de dire à la MMU de passer d'une table à l'autre quand le processeur change de tâche. Chaque programme travaille dans sa zone mémoire.

Pour être sûr qu'une application n'écrase pas les données d'une autre et parer tout bug ou attaque, on cloisonne la mémoire en désactivant ou en cachant les tables de traduction d'adresses des autres application pendant que l'une d'elles est en train de s'exécuter. Pour cela on utilise les niveaux de droits présentés dans la page précédente.

Tables de traduction

La MMU gère deux types de tables de traduction, qui sont situés en mémoire. Ces tables contiennent des descripteurs de segment qui permettent de retrouver rapidement un segment et les privilèges nécessaires pour y accéder. Chaque descripteur est sur 64 bits.

structure d'un descripteur de segment

GDT : Global Descriptor Table

La GDT est unique et comme son nom l'indique a pour vocation d'être globale à tout le système et à changer le moins possible durant la vie du système. Elle contiendra en principe les zones d'adresses constantes d'une tâche à une autre. Elle pourra par exemple contenir les segments de code et de données pouvant être partagés par toutes et parties des tâches, telles que le code / données de l'OS, le code / données des programmes et bibliothèques chargées en mémoire.

Cette table commence toujours par un descripteur NULL (64 bits à 0), puis suivent les autres descripteurs quel que soit l'ordre. Il faut que tous ces descripteurs soit placés de façon contiguës dans la mémoire.

LDT : Local Descriptor Table

Les LDT ont pour vocation à être propres à chaque tâche. Il y a donc une LDT par programme. On peut cependant, si le système d'exploitation le permet, partager une LDT entre plusieurs programmes ou n'utiliser que la GDT

Registres utiles

Pour stocker ces tables ou les retrouver il existe deux registres importants : gdtr (pour la GDT) et lldtr pour la LDT courante. Ces registres sont sur 48 bits avec l'adresse de la table sur 32 bits et la taille de la table sur 16 bits.

Pour réaliser ces opérations des instructions en assembleur existe :